|

"Е14": организация памяти

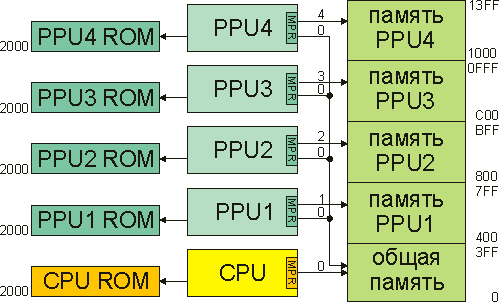

Для удобства разделения памяти между процессорами, в "Е14" используется классический метод страничной адресации. Его механизм проиллюстрирован на рисунке.

Суть страничного метода сводится к следующему. Каждый процессор имеет собственное (локальное) адресное пространство. В "Е14" разрядность адреса установлена в 10 бит, что соответствует объему страницы ОЗУ, равному 100 0000 00002 = 40016 = 102410 байт = 1 Кбайт. К локальному адресу в старшие биты добавляется номер страницы, который у каждого PPU хранится в специальном регистре MPR (Memory Page Register). В итоге мы получаем 10+3 = 13-битный физический адрес.

Особо подчеркнем, что благодаря страничному методу локальная адресация у PPU одинакова (адреса меняются от 0 до 3FF), так что программы для всех периферийных процессоров можно сделать идентичными.

В "Е14" имеется 5 (по числу процессоров) страниц ОЗУ с номерами от 0 до 4. Заметим, что формально можно считать страницы независимыми (находящимися "в разных виртуальных микросхемах"), что разрешает одновременное обращение к каждой из них "своего" процессора. Это автоматически позволяет избежать конфликтов, связанных с одновременным обращением к памяти. Данное требование важнее, чем кажется на первый взгляд: не забывайте, что каждая команда начинается со считывания ее из ОЗУ, так что в начале каждой операции все 5 процессоров "дружно" обращаются к памяти за очередной инструкцией.

Работа со страницами ОЗУ организована следующим образом (см. рисунок).

В центральной части рисунка вы видите процессоры, каждый из которых имеет регистр MPR. Регистр этот может принимать только два значения: 0 и целое число, равное номеру процессора (0 – CPU, 1 – PPU1, … 4 – PPU4). Это означает, что каждый PPU может подключить либо свою собственную страницу, либо нулевую (общую). Очевидно, что CPU, номер которого равен 0, всегда подключен к нулевой странице. Предлагаемый механизм гарантирует каждому PPU собственную страницу ОЗУ, а также потенциальную возможность доступа к общей (нулевой) странице. Данная возможность позволяет изучать архитектуру с общей памятью, но она не используется в архитектуре с распределенной памятью.

Кроме ОЗУ, каждый процессор, начиная с локального адреса 2000, имеет ПЗУ. ПЗУ у всех PPU идентичны; в них записаны основные программы обмена данными между CPU и PPU. Благодаря этим программам PPU способен принимать программу и данные сразу после запуска. Еще ПЗУ обеспечивает переключение страниц ОЗУ, ибо, невозможно, выполняя программу на странице ОЗУ, отключать эту страницу. Что касается CPU, то его ПЗУ содержит программу загрузки шестнадцатеричных кодов из файла и их рассылки в нужные процессоры.

Возможно, описанная система взаимодействия узлов показалась вам слишком сложной. В свое оправдание могу сказать, что используемые механизмы обмена не содержат по своей сути ничего нового по сравнению с одиночным компьютером: шины и порты там тоже имеются. Но зато у модели «Е14» есть важное достоинство: она способна имитировать две параллельных архитектуры – с общей и с распределенной памятью.